# μPD8237A HIGH-PERFORMANCE PROGRAMMABLE DMA CONTROLLER

# **Description**

The  $\mu$ PD8237A high performance DMA controller is a peripheral interface circuit for microprocessor systems. It is designed to improve system performance by allowing external devices to directly transfer information to or from the system memory. Memory-to-memory transfer capability is also provided. The  $\mu$ PD8237A offers a wide variety of programmable control features to enhance data throughput and allow dynamic reconfiguration under program control.

The  $\mu$ PD8237A is designed to be used with an external 8-bit address register such as the 8282. It contains four independent channels and may be expanded to any number of channels by cascading additional controller chips.

The three basic transfer modes allow the user to program the types of DMA service. Each channel can be individually programmed to autoinitialize to its original condition following an end of process (EOP).

Each channel has a full 64K-byte address and word count capability.

# Features

- ☐ Memory-to-memory transfers

- ☐ Memory block initialization

- ☐ Address increment or decrement

- ☐ Four independent DMA channels

- Multiple transfer modes: block, demand, single word, cascade

- ☐ Independent autoinitialization of all channels

- □ Enable/disable control of individual DMA requests

□ Independent polarity control of DREQ and DACK

- signals

- ☐ End of process input for terminating transfers☐ Software DMA requests

- ☐ High performance: transfers up to 1.6 Mbs

- $\hfill \Box$  Directly expandable to any number of channels

#### Ordering Information

| Part        | Package            | Max Frequency |

|-------------|--------------------|---------------|

| Number      | Type               | of Operation  |

| μPD8237AC-5 | 40-pin plastic DIP | 5 MHz         |

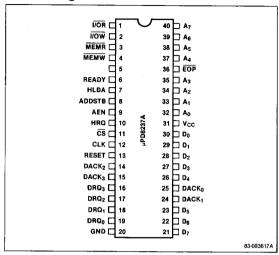

# **Pin Configuration**

### Pin Identification

| No.              | Symbol                                                                         | Function                 |

|------------------|--------------------------------------------------------------------------------|--------------------------|

| 1                | I/OR                                                                           | I/O read control signal  |

| 2                | 1/0W                                                                           | I/O write control signal |

| 3 4              | MEMR                                                                           | Memory read output       |

| 4                | MEMW                                                                           | Memory write output      |

| 5                | _                                                                              | Fixed, high level input  |

| 6                | READY                                                                          | Ready input              |

| 7                | HLDA                                                                           | Hold acknowledge input   |

| 8                | ADDSTB                                                                         | Address strobe output    |

| 9                | AEN                                                                            | Address enable output    |

| 10               | HRQ                                                                            | Hold request output      |

| 11               | CS                                                                             | Chip select input        |

| 12               | CLK                                                                            | Clock input              |

| 13               | RESET                                                                          | Reset input              |

| 14, 15<br>24, 25 | DACK <sub>2</sub> , DACK <sub>3</sub><br>DACK <sub>1</sub> , DACK <sub>0</sub> | DMA acknowledge output   |

| 16-19            | DRQ3-DRQ0                                                                      | DMA request input        |

| 20               | GND                                                                            | Ground                   |

| 21-23,<br>26-30  | D <sub>7</sub> -D <sub>5</sub><br>D <sub>4</sub> -D <sub>0</sub>               | I/O data bus             |

| 31               | V <sub>CC</sub>                                                                | Power supply             |

| 32-35            | A <sub>0</sub> -A <sub>3</sub>                                                 | I/O address bus          |

| 36               | EOP                                                                            | 1/0 end of process       |

| 37-40            | A <sub>4</sub> -A <sub>7</sub>                                                 | Output address bus       |

| 31-40            | M4-M7                                                                          | Output address Dus       |

# **Pin Functions**

### D<sub>0</sub>-D<sub>7</sub> (I/O Data Bus)

During an I/O read, the CPU enables these lines as outputs, allowing it to read an address register, a word count register, or the status or temporary register. During an I/O write, these lines are enabled as inputs, allowing the CPU to program the  $\mu$ PD8237A control registers. During DMA cycles, the eight MSBs of the address are output to the data bus to be strobed to an external latch via ADDSTB.

# A<sub>4</sub>-A<sub>7</sub> (Output Address Bus)

These lines, active only during DMA service, are outputs that provide the four MSBs of the address.

### A<sub>0</sub>-A<sub>3</sub> (I/O Address Bus)

During DMA active states, these lines are outputs that provide the 4 LSBs of the output address bus. During DMA idle states, these lines are inputs, allowing the CPU to load or examine control registers.

#### DRQ<sub>0</sub>-DRQ<sub>3</sub> (DMA Request Input)

These are asynchronous channel request inputs used by peripherals to request DMA service. In a fixed priority scheme, DRQ<sub>3</sub> has the lowest. The polarity of these lines is programmable; however, reset initializes them to active high.

# **HLDA (Hold Acknowledge)**

Indicates that the CPU has relinquished control of the system buses.

# **HRQ (Hold Request)**

Requests control of the system bus. The  $\mu$ PD8237A issues this signal in response to software requests or DRQ inputs from peripherals.

### DACK<sub>0</sub>-DACK<sub>3</sub> (DMA Acknowledge Output)

These lines indicate an active channel. They are sometimes used to select a peripheral. Only one DACK may be active at any time. All DACK lines are inactive unless DMA has control of the bus. The polarity of these lines is programmable; however, reset initializes them to active low.

# **EOP** (End of Process)

$\overline{\text{EOP}}$  signals that DMA service has been completed. When the word count of a channel becomes zero, the  $\mu\text{PD8237A}$  pulses  $\overline{\text{EOP}}$  low to notify the peripheral that DMA service is complete. The peripheral may pull  $\overline{\text{EOP}}$  low to prematurely end DMA service. Internal or external receipt of  $\overline{\text{EOP}}$  causes the currently active channel to end service, set its TC bit in the status register, and reset its request bit. If the channel is programmed for autoinitialization, the current registers are updated from the base registers. Otherwise, the channel's mask bit is set and the contents of the register are unaltered.

EOP is output when TC for channel 1 occurs during memory-to-memory transfers. EOP applies to the channel with an active DACK. When DACK<sub>0</sub>-DACK<sub>3</sub> are inactive, external EOPs are ignored.

Use of an external pull-up resistor of 3.3 k $\Omega$  or 4.7 k $\Omega$  is recommended. This pin ( $\overline{\text{EOP}}$ ) cannot sink the current passed by a 1 k $\Omega$  or 4.7 k $\Omega$  pull-up.

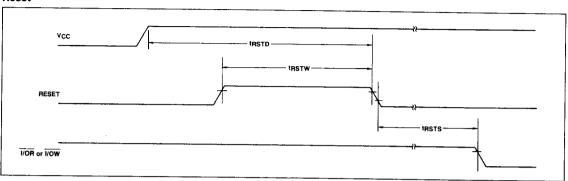

#### RESET

Clears the command, status, request, and temporary registers, the first/last flip flop, and sets the mask register. The  $\mu$ PD8237A is in idle state after a reset.

# CS (Chip Select)

The CPU uses  $\overline{\text{CS}}$  to select the  $\mu\text{PD8237A}$  as an I/O device during an I/O read or write by the CPU. This provides CPU communication on the data bus.  $\overline{\text{CS}}$  may be held low during multiple transfers to or from the  $\mu\text{PD8237A}$  as long as  $\overline{\text{I/OR}}$  or  $\overline{\text{I/OW}}$  is toggled following each transfer.

#### READY

This signal can extend memory read and write pulses for slow memories or I/O peripherals.

#### CLK (Clock)

Controls internal operations and data transfer rate.

### **AEN (Address Enable)**

This signal allows the external latch to output the upper address byte by disabling the system bus during DMA cycles. Use HLDA and AEN to deselect I/O peripherals that may be erroneously accessed during DMA transfers. The  $\mu$ PD8237A deselects itself during DMA transfers.

# ADDSTB (Address Strobe)

This signal strobes the upper address byte form D<sub>0</sub>-D<sub>7</sub> into an external latch.

# **MEMR** (Memory Read)

This signal accesses data from a specified memory location during memory-to-peripheral or memory-to-memory transfers.

# **MEMW** (Memory Write)

This signal writes data to a specified memory location during peripheral-to-memory or memory-to memory transfers.

# I/OR (I/O Read)

In the idle state, this signal is an input control line used by the CPU to read control registers. In the active state, the  $\mu$ PD8237A uses  $\overline{I/OR}$  as an output control signal to access data from a peripheral during a DMA write.

# I/OW (I/O Write)

In the idle state, the CPU uses  $\overline{I/OW}$ , as an input control signal to load information to the  $\mu PD8237A$ . In the active state, the  $\mu PD8237A$  uses  $\overline{I/OW}$  as an output control signal to load data to a peripheral during a DMA read.

The rising edge of  $\overline{WR}$  must follow each data byte transfer in order for the CPU to write to the  $\mu$ PD8237A. Holding  $\overline{I/OW}$  low while toggling  $\overline{CS}$  does not produce the same effect.

### Pin 5

Pin 5 is always tied high.

# Vcc

Power supply.

#### **GND**

Ground.

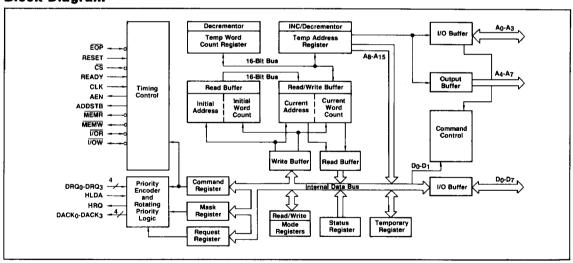

# **Block Diagram**

# **Functional Description**

The  $\mu$ PD8237A has three basic control logic blocks, as shown in the block diagram. The command control block decodes commands issued by the CPU to the  $\mu$ PD8237A before DMA requests are serviced. It also decodes the mode control word of each channel. The timing control block generates the external control signals and the internal timing. The priority encoder block settles priority contentions among channels simultaneously requesting service.

# **DMA Operation**

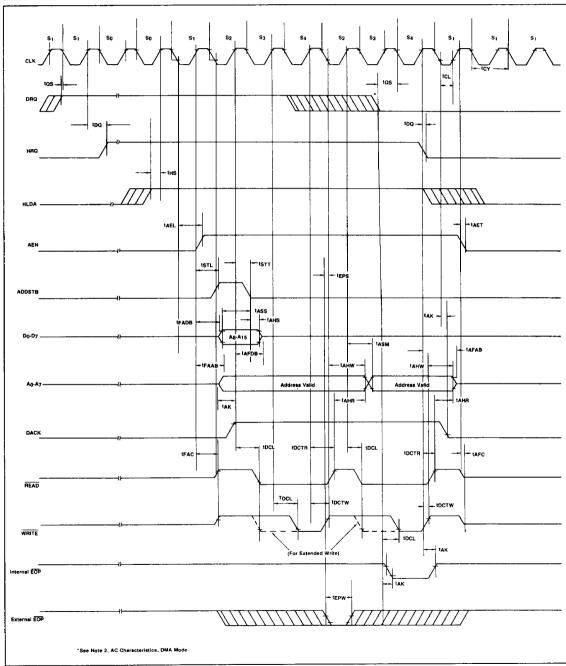

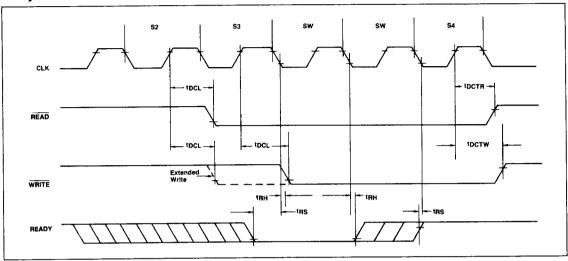

The  $\mu$ PD8237A operates in two states: idle and active. Each of these is made up of several smaller states equal to one clock cycle. The inactive state, S1, is entered when there are no pending DMA requests. The controller is inactive in S1, but the CPU may program it. S0 is the initial state for DMA service; the  $\mu$ PD8237A requests a hold, but the CPU has not acknowledged. Transfers may begin upon acknowledgement from the CPU. The normal working states of DMA service are S1, S2, S3, and S4. If more time is needed for a transfer, a wait state, SW, can be inserted using the READY line.

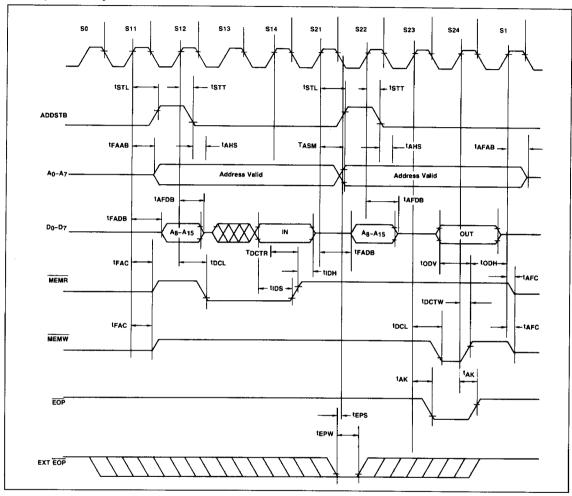

A memory-to-memory transfer requires read-frommemory and write-to-memory operations. The states S11, S12, S13, and S14 provide the read-from operation. S21, S22, S23, and S24 provide the write-to part of the transfer. The byte is stored in the temporary register between operations.

#### Idle State

When there are no pending service requests, the  $\mu\text{PD8237A}$  is in the idle state; more specifically, in S1, DRQ lines and  $\overline{\text{CS}}$  are sampled to determine requests for DMA service and CPU attempts to inspect or modify the registers of the  $\mu\text{PD8237A}$ , respectively. The CPU can read or write to the registers when  $\overline{\text{CS}}$  and HLDA are low.  $A_0\text{-}A_3$  are used as inputs to the  $\mu\text{PD8237A}$  and select the registers affected. The  $\overline{I/\text{OR}}$  and  $\overline{I/\text{OW}}$  lines select and time the reads and writes. An internal flip-flop generates an additional address bit which determines the upper or lower byte of the address and word count registers. This flip-flop can be reset by master clear, reset, or a software command.

When  $\overline{\text{CS}}$  and HLDA are low (program phase), the  $\mu\text{PD8237A}$  can execute special software commands. When  $\overline{\text{CS}}$  and  $\overline{\text{I/OW}}$  are active, the commands are decoded as addresses and do not use the data bus.

#### **Active State**

When a channel requests service while the  $\mu$ PD8237A is in idle state, the  $\mu$ PD8237A outputs an HRQ to the CPU and enters the active state. DMA service takes place in the active state, in one of the four modes described below.

DRQ is held active only until the corresponding DACK goes active when a single transfer is performed. If DRQ is held active for a longer period, HRQ will become inactive after each transfer, become active again, and a one-byte transfer will be made after each rising edge of HLDA. This assures a full machine cycle between DMA transfers in 8080A/8085A systems. Timing between the  $\mu$ PD8237A and other bus control protocols depends on the CPU being used.

#### **Block Transfer Mode**

In this mode, the  $\mu$ PD8237A makes transfers until it encounters a TC or an external  $\overline{EOP}$ . Hold DRQ active only until DACK goes active. The channel will autoinitialize at the end of the DMA service if it has been programmed to do so.

#### **Demand Transfer Mode**

In this mode, the  $\mu PD8237A$  makes transfers until it encounters a TC or an external  $\overline{EOP}$ , or until DRQ becomes inactive. This allows the device requesting service to stop the transfers by sending DRQ inactive. The device can resume service by making DRQ active. The current address and current word count registers may be examined during the time between services when the CPU is allowed to operate. Autoinitialization can occur only after a TC or  $\overline{EOP}$  at the end of the DMA service. After an autoinitialization, there must be an active-going DRQ edge to begin new DMA service.

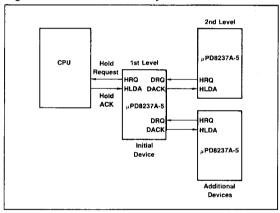

### Cascade Mode

In this mode, you can expand your system by cascading several  $\mu$ PD8237As together. Connect the HLDA and HRQ signals from the additional  $\mu$ PD8237As to the DRQ and DACK signals of a channel of the initial  $\mu$ PD8237A. This scheme allows the additional devices to send the DMA requests through the priority resolution circuitry of the preceding device, preserving the priority chain and forcing the device to wait its turn to acknowledge requests. The cascade channel in the initial device does not output any address or control signals because its only function is that of assigning priorities. The  $\mu$ PD8237A responds to DRQ with DACK, but all outputs except HRQ are disabled.

Figure 1 shows two  $\mu$ PD8237As cascaded into two channels of another one, forming a two-level DMA system. You could add more devices at the second level by using the leftover channels of the first level; likewise, you could add more devices to form a third level by cascading into the channels of the second level.

#### **Transfers**

There are three types of transfers that can be performed by the three active transfer modes: read, write, and verify. Read transfers activate MEMR and I/OW to move memory data to an I/O device. Write transfers activate I/OR and MEMW to move data from an I/O device to memory. Verify transfers are not really transfers; the µPD8237A goes through the motions of a transfer but the memory and I/O lines are not active.

Figure 1. Two-Level DMA System

# **Memory-to-Memory Transfers**

Use block transfer mode for memory-to-memory transfers. Mask out channels 0 and 1, and initialize the channel 0 word count to the same value as channel 1. Setting bit C0 of the command register to 1 makes channels 0 and 1 operate as memory-tomemory transfer channels. Channel 0 is the source address, channel 1 is the destination address, and the channel 1 word count is used. Initiate the memory-tomemory transfer by setting a DMA request for channel 0. You can write a single source word to a block of memory when channel 0 is programmed for a fixed source address. The µPD8237A responds to external EOP signals during these transfers, but no DACK outputs are active. The EOP input may be used by data comparators doing block searches to end service when a match is found.

#### Autoinitialization

A channel may be set for autoinitialize by programming a bit in the mode register. Autoinitialize restores the original values of the current address and current word count registers from the initial address and initial word count registers of that channel. The CPU loads the current and initial registers simultaneously and they are unchanged through DMA service. EOP does not set the mask bit when the channel is in autoinitialize. The channel can repeat its service following autoinitialize without CPU intervention.

# **Priority Resolution**

Two software-selectable priority resolution schemes are available on the  $\mu PD8237A$ : fixed priority and rotating priority. In the fixed priority scheme, priority is assigned by the value of the channel number. Channel 3 is the lowest priority and channel 0 is the highest priority.

In the rotating priority scheme, the channel that was just serviced assumes the lowest priority and the other channels move up accordingly. This guarantees that a device requesting service can be adcknowledged after no more than three other devices have been serviced, preventing any channel from monopolizing the system.

The highest priority channel is selected on each active-going HLDA edge. Once service to a channel begins, it cannot be interrupted by a request from a higher priority channel. A higher priority channel gets control only when the lower priority channel releases HRQ. The CPU gets bus control when control passes from channel to channel, ensuring that a rising HLDA edge can be generated to select the new highest priority request.

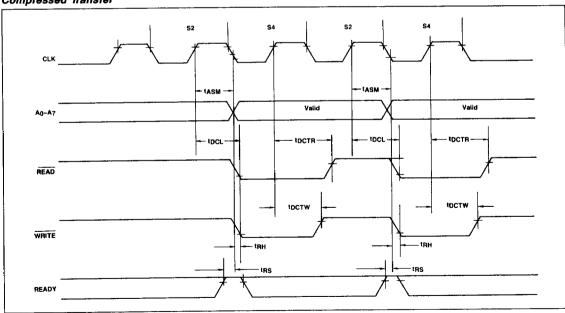

### Transfer Timing

If, you can cut transfer timing, by compressing the transfer time to two clock periods. Since state 3 (S3) extends the access time for the read pulse, you can eliminate S3, making the width of the read pulse equal to the write pulse. A transfer is then made up of S2 to change the address and S4 to perform the read or write. When the address lines A<sub>8</sub>-A<sub>15</sub> need to be updated, S1 states occur.

# **Generating Addresses**

The eight MSBs of the address are multiplexed on the data lines. These bits are output to an external latch during S1, after which they can be placed on the address bus. The falling edge of ADDSTB loads the bits from the data lines to the latch. AEN places the bits on the address bus. The eight LSBs of the address are directly output on lines A<sub>0</sub>-A<sub>7</sub> to the address bus.

Sequential addresses are generated during block and demand transfer mode operations because they include several transfers. Often, data in the external address latch does not change; it changes only when a carry or borrow from  $A_7$  to  $A_8$  occurs in the sequence of addresses. S1 states are executed only when  $A_8$ - $A_{15}$  need to be updated. In the course of lengthy transfers, S1 states may be executed only once every 256 transfers.

# Registers

Table 1 summarizes the registers of the µPD8237A.

Table 1. Register Summary

| Register                      | No. | Bits |

|-------------------------------|-----|------|

| Current address registers     | 4   | 16   |

| Current word count registers  | 4   | 16   |

| Initial address registers     | 4   | 16   |

| Initial word count registers  | 4   | 16   |

| Command register              | 1   | 8    |

| Mode registers                | 4   | 6    |

| Request register              | 1   | 4    |

| Mask register                 | 1   | 4    |

| Status register               | 1   | 8    |

| Temporary register            | 1   | 8    |

| Temporary address register    | 1   | 16   |

| Temporary word count register | 1   | 16   |

Current Address Register. There is a current address register for each channel. This register holds the address used for DMA transfers; the address is incremented or decremented after each transfer and the intermediate values are stored here during the transfer. The CPU writes or reads this register in 8-bit bytes. An autoinitialize restores this register to its initial value.

Current Word Count Register. There is a current word count register for each channel. Program this register with the value of the number of words to be transferred, minus one. The word count is decremented after each transfer and intermediate values are stored in this register during the transfer. A TC is generated when the word count is zero. The CPU writes or reads this register in 8-bit bytes during program phase. An autoinitialize restores this register to its initial value. After an internally generated EOP, the contents of this register with be FFFFH.

Initial Address and Initial Word Count Registers. There is an initial register and an initial word count register for each channel. The initial values of the associated current registers are stored in these registers. The values in these registers are used to restore the current registers at autoinitialize. During DMA programming, the CPU writes the initial registers and the corresponding current registers at the same time, in 8-bit bytes. Intermediate values in the current registers are overwritten if you write to the initial registers while the current registers contain intermediate values. The CPU cannot read the initial registers.

Table 2. Word Count and Address Register Command Codes

|                            | Operation                  |    |          |              | Internal       |                |                |                |           |                                                                   |

|----------------------------|----------------------------|----|----------|--------------|----------------|----------------|----------------|----------------|-----------|-------------------------------------------------------------------|

| Channel                    |                            | CS | I/OR     | I/OW         | A <sub>3</sub> | A <sub>2</sub> | A <sub>1</sub> | A <sub>0</sub> | Flip-Flop | D <sub>0</sub> -D <sub>7</sub>                                    |

| )                          | Initial & current          | 0  | 1        | 0            | 0              | 0              | 0              | 0              | 0         | A <sub>0</sub> -A <sub>7</sub>                                    |

|                            | address write              | 0  | 1        | 0            | . 0            | 0              | 0              | 0              | 1         | A <sub>8</sub> -A <sub>15</sub>                                   |

|                            | Current                    | 0  | 0        | 1            | 0              | 0              | 0              | 0              | 0         | A <sub>0</sub> -A <sub>7</sub>                                    |

|                            | address read               | 0  | 0        | 11           | 0              | 0              | 0              | 0              | 1         | A <sub>8</sub> -A <sub>15</sub>                                   |

|                            | Initial & current          | 0  | 1        | 0            | 0              | 0              | 0              | 1              | 0         | $W_0-W_7$                                                         |

|                            | word count write           | 0  | 1        | 0            | 0              | 0              | 0              | 1              | 1         | W8-W <sub>15</sub>                                                |

|                            | Current                    | 0  | 0        | 1            | 0              | 0              | 0              | 1              | 0         | $W_0-W_7$                                                         |

|                            | word count read            | 0  | 0        | 1            | 0              | 0              | 0              | 1              | 1         | W <sub>8</sub> -W <sub>15</sub>                                   |

|                            | Initial & current          | 0  | 1        | 0            | 0              | 0              | 1              | 0              | 0         | A <sub>0</sub> -A <sub>7</sub>                                    |

|                            | address write              | 0  | 1        | 0            | 0              | 0              | 1              | 0              | 1         | A8-A <sub>15</sub>                                                |

|                            | Current                    | 0  | 0        | 1            | 0              | 0              | 1              | 0              | 0         | A <sub>0</sub> -A <sub>7</sub>                                    |

|                            | address read               | 0  | 0        | 1            | 0              | 0              | 1              | 0              | 1         | A <sub>8</sub> -A <sub>15</sub>                                   |

|                            | Initial & current          | 0  | 1        | 0            | 0              | 0              | 1              | 1              | 0         | Wn-Wz                                                             |

|                            | word count write           | 0  | 1        | 0            | 0              | 0              | 1              | 1              | 1         | W8-W <sub>15</sub>                                                |

| Current<br>word count read | Current                    | 0  | 0        | 1            | 0              | 0              | 1              | 1              | 0         | W <sub>0</sub> -W <sub>7</sub>                                    |

|                            |                            | Ö  | Ō        | 1            | ō              | Ö              | 1              | i              | ĭ         | W <sub>8</sub> -W <sub>15</sub>                                   |

|                            | Initial & current          | 0  | 1        | 0            | 0              | 1              | 0              | 0              | 0         | A <sub>0</sub> -A <sub>7</sub>                                    |

| -                          | address write              | Ō  | 1        | Ö            | Ō              | 1              | ō              | Ŏ              | 1         | A <sub>8</sub> -A <sub>15</sub>                                   |

|                            | Current                    | 0  | 0        | 1            | 0              | 1              | 0              | 0              | 0         | A <sub>0</sub> -A <sub>7</sub>                                    |

|                            | address read               | Ō  | Ō        | 1            | Ō              | 1              | Ö              | ŏ              | ĭ         | Ag-A <sub>15</sub>                                                |

|                            | Initial & current          | 0  | 1        | 0            | 0              | 1              | 0              | 1              | 0         | W <sub>0</sub> -W <sub>7</sub>                                    |

|                            | word count write           | ŏ  | i        | Ö            | Ŏ              | i              | ŏ              | i              | 1         | W <sub>8</sub> -W <sub>15</sub>                                   |

|                            | Current                    | 0  | 0        | 1            | 0              | 1              | 0              | 1              | 0         | W <sub>0</sub> -W <sub>7</sub>                                    |

|                            | word count read            | ő  | Õ        | i            | Ö              | i              | Ö              | 1              | 1         | W <sub>8</sub> -W <sub>15</sub>                                   |

|                            | Initial & current          | 0  | 1        | 0            | 0              | 1              | 1              | 0              | 0         | A <sub>0</sub> -A <sub>7</sub>                                    |

|                            | address write              | 0  | i        | 0            | 0              | i              | 1              | 0              | 1         | A <sub>0</sub> -A <sub>7</sub><br>A <sub>8</sub> -A <sub>15</sub> |

|                            | Current                    | 0  | 0        | 1            | 0              | 1              | 1              | 0              |           |                                                                   |

|                            | address read               | 0  | 0        | 1            | 0              | 1              | 1              | 0              | 0<br>1    | A <sub>0</sub> -A <sub>7</sub><br>A <sub>8</sub> -A <sub>15</sub> |

|                            | Initial & current          | 0  | 1        | <del>'</del> | 0              | 1              | 1              | 1              |           |                                                                   |

|                            | word count write           | 0  | 1        | 0            | 0              | 1              | 1              | 1              | 0         | W <sub>0</sub> -W <sub>7</sub><br>W <sub>8</sub> -W <sub>15</sub> |

|                            |                            |    |          |              |                |                |                | <del></del>    |           |                                                                   |

|                            | Current<br>word count read | 0  | 0        | 1            | 0              | 1              | 1              | 1              | 0<br>1    | W <sub>0</sub> -W <sub>7</sub>                                    |

|                            | word count read            | U  | <u> </u> | 1            | U              | 1              |                | 1              |           | W <sub>0</sub> -W <sub>15</sub>                                   |

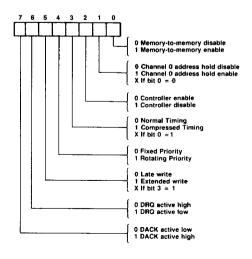

Command Register. The CPU programs this register during program phase. The register can be cleared with reset.

Mode Register. There is a mode register associated with each channel. When the CPU writes to this register during the program phase, bits 0 and 1 determine on which channel mode register the operation is performed.

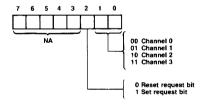

Request Register. This register allows the  $\mu$ PD8237A to respond to DMA requests from software as well as hardware. There is a bit pattern for each channel in the request register. These bits can be prioritized by the priority resolving circuitry and are not maskable. Each bit is set or reset under software control or cleared when TC or an external  $\overline{\text{EOP}}$  is generated. A reset clears the entire register. The correct data word is loaded by software to set or reset a bit.

Software requests receive service only when the channel is in block mode. The software request for channel 0 should be set at the beginning of a memory-tomemory transfer.

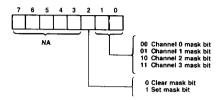

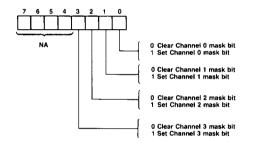

Mask Register. There is a mask bit for each channel which can disable an incoming DRQ. If the channel is not set for autoinitialize, each mask bit is set when its channel produces an EOP. Each bit can be set or cleared under software control. Reset clears the register. This disallows DMA requests until they are permitted by a clear mask register instruction.

You may also write all four bits of the mask register with a single command.

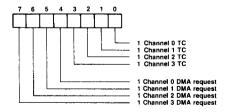

Status Register. The status register indicates which channels have made DMA requests and which channels have reached TC. Each time a channel reaches TC, including after autoinitialization, bits 0-3 are set. Status read and reset clear these bits. Bits 4-7 are set when a channel is requesting service. The CPU can read the status register.

Temporary Register. The temporary register holds data during memory-to-memory transfers. The CPU can read the last word moved when the transfer is complete. This register always contains the last byte transferred in a memory-to-memory transfer unless cleared by a reset.

#### Software Commands

There are two software commands that can be executed in the program phase. These commands are independent of data on the data bus.

Clear First/Last Flip-Flop. You may issue this command before reading or writing any word count or address information. It allows the CPU to access registers, addressing upper and lower bytes correctly by initializing the flip-flop to an identifiable state.

Master Clear. This command produces the same effect as reset. It clears the command, status, request, temporary, and internal first/last flip-flop registers, sets the mask register, and causes the  $\mu PD8237A$  to enter idle state.

Table 3 illustrates address codes for the software commands.

Table 3. Software Command Codes

| A <sub>3</sub> | A <sub>2</sub> | A <sub>1</sub> | Ao | I/OR | 170W | (1) Operation                |

|----------------|----------------|----------------|----|------|------|------------------------------|

| 1              | 0              | 0              | 0  | 0    | 1    | Read status register         |

| 1              | 0              | 0              | 0  | 1    | 0    | Write to command register    |

| 1              | 0              | 0              | 1  | 1    | 0    | Write to request register    |

| 1              | 0              | 1              | 0  | 1    | 0    | Write a mask register bit    |

| 1              | 0              | 1              | 1  | 1    | 0    | Write to mode register       |

| 1              | 1              | 0              | 0  | 1    | 0    | Clear byte pointer flip-flop |

| 1              | 1              | 0              | 1  | 0    | 1    | Read temporary register      |

| 1              | 1              | 0              | 1  | 1    | 0    | Master clear                 |

| 1              | 1              | 1              | 1  | 1    | 0    | Write all mask register bits |

| 1              | 1              | 1              | 0  | 0    | 1    | Clear Mask register          |

#### Note

(1) All other bit combinations are illegal.

# **Application Example**

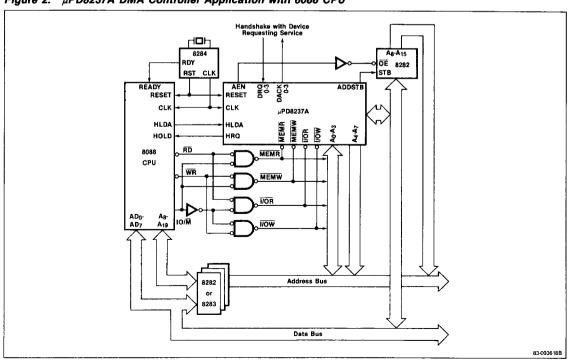

Figure 2 shows an application using the  $\mu$ PD8237A with an 8088. The  $\mu$ PD8237A sends a hold request to the CPU whenever there is a valid DMA request from a peripheral device. The  $\mu$ PD8237A takes control of the address, data, and control buses when the CPU

Figure 2. µPD8237A DMA Controller Application with 8088 CPU

replies with an HLDA signal. The address for the first transfer appears in two bytes: the eight LSBs are output on  $A_0$ - $A_7$  and the eight MSBs are output on the data bus pins. The contents of the data bus pins are latched to the 8282 to make up the 16 bits of the address bus. Once the address is latched, the data bus transfers data to or from a memory location or I/O device, using the control bus signals generated by the  $\mu$ PD8237A.

# **AC Characteristics Supplementary Information**

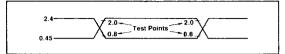

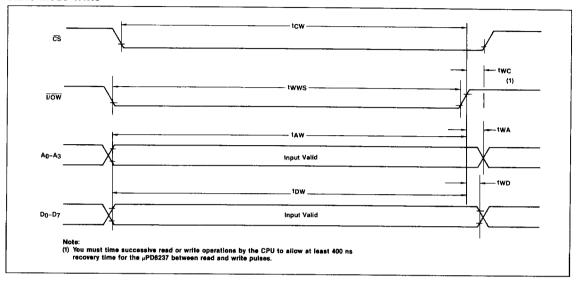

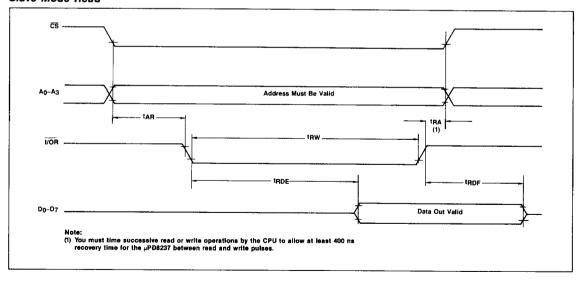

All AC timing measurement points are 2.0 V for high and 0.8 V for low, for both inputs and outputs. The loading on the outputs is one TTL gate plus 100 pF of capacitance for the data bus pins, and one TTL gate plus 50 pF for all other outputs.

Recovery time between successive read and write inputs must be at least 400 ns. I/O or memory write pulse widths will be  $T_{CY}\text{-}100$  ns for normal DMA transfers and 2  $T_{CY}\text{-}100$  ns for extended cycles. I/O or memory reads will be 2  $T_{CY}\text{-}50$  ns for normal reads and  $T_{CY}\text{-}50$  ns for compressed cycles.  $T_{DQ1}$  and  $T_{DQ2}$  are measured on two different levels:  $T_{DQ1}$  at 2.0 V,  $T_{DQ2}$  at 3.3 V with a 3.3 k $\Omega$  pull-up resistor. DREQ and DACK are both active high and low. DREQ must be held in the active state (user defined) until DACK is returned from the  $\mu\text{PD8237A}$ . The AC waveforms assume these are programmed to the active high state.

#### **Absolute Maximum Ratings**

$T_A = 25^{\circ}C$

| Ambient temperature under bias,       |                 |

|---------------------------------------|-----------------|

| T <sub>OPT</sub>                      | 0°C to +70°C    |

| Storage temperature, T <sub>STG</sub> | -65°C to +150°C |

| Voltage on any pin with respect to    |                 |

| Ground, V <sub>CC</sub>               | -0.5V to +7V    |

| Power dissipation, PD                 | 1.5 W           |

Comment: Exposing the device to stresses above those listed in Absolute Maximum Ratings could cause permanent damage. The device is not meant to be operated under conditions outside the limits described in the operational sections of this specification. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# Capacitance

$T_A = 25^{\circ}C$

|                    |                |     | Limits             |     | Test |                        |  |

|--------------------|----------------|-----|--------------------|-----|------|------------------------|--|

| Parameter          | Symbol         | Min | Typ <sup>(1)</sup> | Max | Unit | Conditions             |  |

| Output capacitance | C <sub>0</sub> |     | 4                  | 8   | pF   | fc = 1.0 MHz,          |  |

| Input capacitance  | CI             |     | 8                  | 15  | pF   | Inputs $= 0 \text{ V}$ |  |

| 1/0 capacitance    | CIO            |     | 10                 | 18  | pF   |                        |  |

#### Note

Typical values measured at T<sub>A</sub> = 25°C, nominal processing parameters, and nominal V<sub>CC</sub>.

# **DC Characteristics**

$T_A = 0$ °C to +70°C;  $V_{CC} = +5 \text{ V } \pm 5\%$

|                           |                 | Limits |                    |                          |      | Test                                         |

|---------------------------|-----------------|--------|--------------------|--------------------------|------|----------------------------------------------|

| Parameter                 | Symbol          | Min    | Typ <sup>(1)</sup> | Max                      | Unit | Conditions                                   |

| Output high               | V <sub>OH</sub> | 2.4    |                    |                          | ٧    | $I_{0H} = -200  \mu A$                       |

| voltage                   |                 | 3.3    |                    |                          | V    | $I_{OH} = -100 \mu A$ (HRQ only)             |

| Output low voltage        | V <sub>OL</sub> |        |                    | 0.45                     |      | I <sub>OL</sub> = 2.0 mA<br>(Data bus)       |

|                           |                 |        |                    |                          | ٧    | I <sub>OL</sub> = 3.2 mA<br>(Other outputs)  |

| Input high voltage        | V <sub>IH</sub> | 2.0    |                    | V <sub>CC</sub><br>+ 0.5 | ٧    |                                              |

| Input low voltage         | V <sub>IL</sub> | -0.5   |                    | 0.8                      | ٧    |                                              |

| Input load<br>current     | lu              |        |                    | ±10                      | μΑ   | OV ≤ V <sub>IN</sub><br>≤ V <sub>CC</sub>    |

| Output leakage<br>current | I <sub>LO</sub> | -      |                    | ±10                      | μΑ   | 0.45 ≤ V <sub>OUT</sub><br>≤ V <sub>CC</sub> |

| V <sub>CC</sub> supply    | lcc             |        | 65                 | 130                      | mA   | $T_A = +25$ °C                               |

| current                   |                 |        | 75                 | 150                      | mΑ   | $T_A = 0$ °C                                 |

## Note:

Typical values measured at T<sub>A</sub> = 25°C, nominal processing parameters, and nominal V<sub>CC</sub>.

# AC Characteristics DMA (Master) Mode

$T_A = 0^{\circ}C \text{ to } + 70^{\circ}C; V_{CC} = 5V \pm 5\%; V_{SS} = 0 \text{ V}$

|                                      |                                                                                                                                                              | Limits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Symbol                               | Min                                                                                                                                                          | Тур                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Max                                           | Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| † <sub>AEL</sub>                     |                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 200                                           | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| taet                                 |                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 130                                           | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| t <sub>AFAB</sub>                    |                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 90                                            | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| <sup>t</sup> AFC                     |                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 120                                           | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| t <sub>AFDB</sub>                    |                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 170                                           | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| tahr                                 | t <sub>CY</sub> - 100                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                               | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| tAHS                                 | 30                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                               | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| tahw                                 | t <sub>CY</sub> -50                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                               | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| tak                                  |                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 170                                           | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| t <sub>AK</sub>                      |                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 170                                           | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| t <sub>AK</sub>                      |                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 100                                           | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| t <sub>ASM</sub>                     |                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 170                                           | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| tass                                 | 100                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                               | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| t <sub>CH</sub>                      | 80                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                               | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| t <sub>CL</sub>                      | 68                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                               | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| t <sub>CY</sub>                      | 200                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                               | пѕ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| <sup>†</sup> DCL                     |                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 190                                           | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| t <sub>DCTR</sub>                    | ,                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 190                                           | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| t <sub>DCTW</sub>                    |                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 130                                           | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| t <sub>DQ1</sub><br>t <sub>DQ2</sub> |                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 120<br>120                                    | ns<br>ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| teps                                 | 40                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| t <sub>EPW</sub>                     | 220                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                               | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| t <sub>FAAB</sub>                    |                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 170                                           | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |