# TDA8133

# 5.1V +8V REGULATOR WITH DISABLE AND RESET

#### ADVANCE DATA

- OUTPUT CURRENTS UP TO 0.75A

- FIXED PRECISION OUTPUT 1 VOLTAGE  $5.1V \pm 2\%$

- FIXED PRECISION OUTPUT 2 VOLTAGE 8V ± 2%

- OUTPUT 1 WITH RESET FACILITY

- OUTPUT 2 WITH DISABLE BY TTL INPUT

- SHORT CIRCUIT PROTECTION AT BOTH OUTPUTS

- THERMAL PROTECTION

- LOW DROP OUTPUT VOLTAGE

#### DESCRIPTION

The TDA8133 is a monolithic dual positive voltage regulator designed to provide fixed precision output voltages of 5.1V and 8V at currents up to 0.75A.

An internal reset circuit generates a reset pulse when the output 1 decrease below the regulated voltage value.

Output 2 can be disabled by TTL input.

Short circuit and thermal protections are included in all the versions.

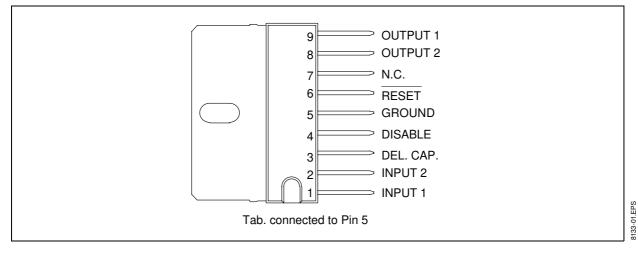

#### **PIN CONNECTIONS**

#### March 1994

This is advance information on a new product now in development or undergoing evaluation. Details are subject to change without notice.

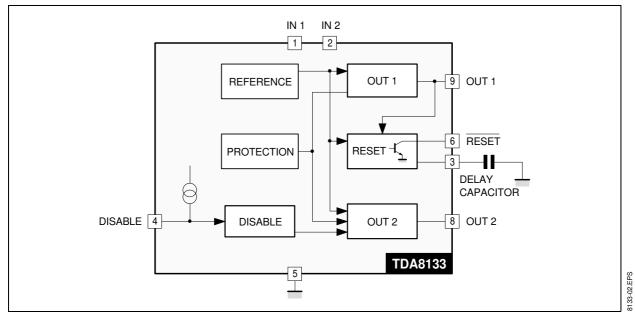

#### **BLOCK DIAGRAM**

#### **ABSOLUTE MAXIMUM RATINGS**

| Symbol            | Parameter               | Value              | Unit |  |

|-------------------|-------------------------|--------------------|------|--|

| V <sub>IN</sub>   | DC Input Voltage Pin 1  | 20                 | V    |  |

| V <sub>DIS</sub>  | Disable Input Voltage   | 20                 | V    |  |

| V <sub>RST</sub>  | Output Voltage at Pin 6 | 20                 | V    |  |

| I <sub>01,2</sub> | Output Currents         | Internally Limited |      |  |

| Pt                | Power Dissipation       | Internally Limited |      |  |

| T <sub>stg</sub>  | Storage Temperature     | -65 to +150        | °C   |  |

| Tj                | Junction Temperature    | 0 to +150          | °C   |  |

#### THERMAL DATA

| Symbol                | Parameter                                   | Value | Unit |

|-----------------------|---------------------------------------------|-------|------|

| R <sub>th (j-c)</sub> | Maximum Thermal Resistance Junction-case    | 8     | °C/W |

| R <sub>th (j-a)</sub> | Maximum Thermal Resistance Junction-ambient | 60    | °C/W |

| Tj                    | Maximum Recommended Junction Temperature    | 130   | °C   |

| Symbol              | Parameter                                        | Test Conditions                                                                                                                | Min.    | Тур.        | Max.       | Unit     |

|---------------------|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|---------|-------------|------------|----------|

| V <sub>01</sub>     | Output Voltage                                   | lo1 = 10mA                                                                                                                     | 5       | 5.1         | 5.2        | V        |

| V <sub>O2</sub>     | Output Voltage                                   | I <sub>O2</sub> = 10mA                                                                                                         | 7.84    | 8           | 8.16       | V        |

| V <sub>O1</sub>     | Output Voltage                                   | 7V < V <sub>IN1</sub> < 14V                                                                                                    |         |             | 5.3        | V        |

| V <sub>O2</sub>     | Output Voltage                                   | 10V < V <sub>IN2</sub> < 14V<br>5mA < I <sub>O1,2</sub> < 750mA                                                                | 7.7     |             | 8.3        | V        |

| V <sub>IO1,2</sub>  | Dropout Voltage I <sub>O1,2</sub> = 750mA        |                                                                                                                                |         |             | 1.4        | V        |

| V <sub>O1,2LI</sub> | Line Regulation                                  | $7V < V_{IN1} < 14V$<br>$10V < V_{IN2} < 14V$<br>$I_{O1,2} = 200mA$                                                            |         |             | 50<br>80   | mV<br>mV |

| V <sub>O1,2LO</sub> | Load Regulation                                  | 5mA < I <sub>O1</sub> < 0.6A<br>5mA < I <sub>O2</sub> < 0.6A                                                                   |         |             | 100<br>160 | mV<br>mV |

| ΙQ                  | Quiescent Current                                | t I <sub>O1</sub> = 10mA<br>Output 2 Disabled                                                                                  |         |             | 2          | mA       |

| V <sub>O1RST</sub>  | Reset Thrseshold Voltage                         | $K = V_{O1}$                                                                                                                   | K - 0.4 | K -<br>0.25 | K - 0.1    | V        |

| V <sub>RTH</sub>    | Reset Thrseshold Hysteresis See circuit descript |                                                                                                                                | 20      | 50          | 75         | mV       |

| t <sub>RD</sub>     | Reset Pulse Delay                                | C <sub>e</sub> = 100nF<br>See circuit description                                                                              |         | 25          |            | ms       |

| $V_{RL}$            | Saturation Voltage in Reset Condition            | I <sub>5</sub> = 5mA                                                                                                           |         |             | 0.4        | V        |

| I <sub>RH</sub>     | Leakage Current in Normal Condition at Pin 6     | V <sub>5</sub> = 10V                                                                                                           |         |             | 10         | μΑ       |

| K01,2               | Output Voltage Thermal Drift                     | $\begin{split} T_{j} &= 0 \text{ to } 125^{o}C \\ K_{O} &= \frac{\Delta V_{O} \cdot 10^{6}}{\Delta T \cdot V_{O}} \end{split}$ | 10      |             |            | ppm/ºC   |

| I <sub>O1,2SC</sub> | Short Circuit Output Current                     | $V_{IN1} = 7V, V_{IN2} = 10V$<br>$V_{IN1,2} = 16V$ (see Note)                                                                  |         |             | 1.6<br>1   | A<br>A   |

| V <sub>DISH</sub>   | Disable Voltage High (out 2 active)              |                                                                                                                                | 2       |             |            | V        |

| V <sub>DISL</sub>   | Disable Voltage Low (out 2 disabled)             |                                                                                                                                |         |             | 0.8        | V        |

| I <sub>DIS</sub>    | Disable Bias Current                             | $0V < V_{DIS} < 7V$                                                                                                            | -100    |             | 2          | μA       |

| T <sub>jsd</sub>    | Junction Temperature for Thermal Shut Down       |                                                                                                                                |         | 145         |            | °C       |

**ELECTRICAL CHRACTERISTICS** ( $V_{IN1} = 7V$ ,  $V_{IN2} = 10V$ ,  $T_j = 25^{\circ}C$ , unless otherwise specified)

Note : Safe permanent short-circuit is only guaranteed for input voltages up to 16V.

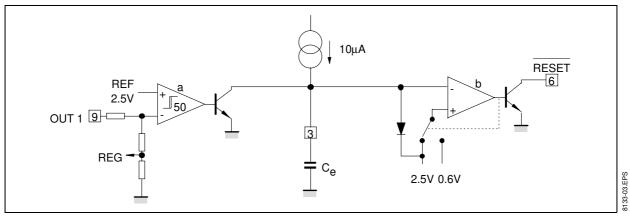

#### **CIRCUIT DESCRIPTION**

The TDA8133 is a dual voltage regulator with Reset and Disable.

The two regulation parts are supplied from one voltage reference circuit trimmed by zener zap during EWS test.

Since the supply voltage of this last is connected at Pin 1 ( $V_{IN1}$ ), the regulator 2 will not work if Pin 1 is not supplied.

The outputs stage have been realized in darlington configuration with a drop typical 1.2V.

The disable circuit, switch-off the output 2 if a voltage lower than 0.8V is applied at Pin 4.

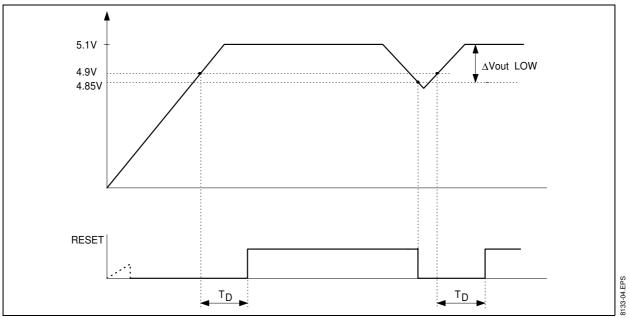

The Reset circuit checks the voltage at the output 1. If this one goes below V<sub>OUT</sub> - 0.25V (4.85V typ.), the comparator "a" (see Figure 1) discharges rapidly the capacitor C<sub>e</sub> and the reset output goes at once Low. When the voltage at the out1 rises above V<sub>OUT</sub> - 0.2V (4.9V typ.), the voltage V<sub>Ce</sub> increases linearly to 2.5V corresponding to a delay td following the law :  $t_1 = \frac{C_e \cdot 2.5V}{10\mu A}$  (see Figure 2), then the reset output goes high again. To avoid gliches in the reset output, the second comparator "b" has a large hysteresis (1.9V).

#### **TDA8133**

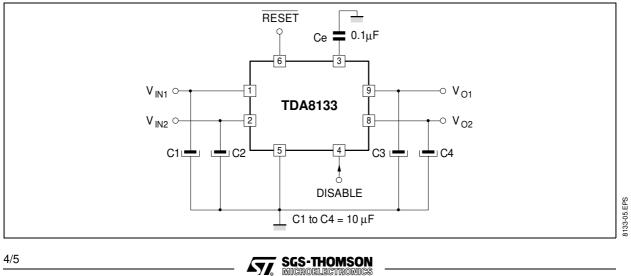

#### Figure 1

# Figure 2

# TYPICAL APPLICATION

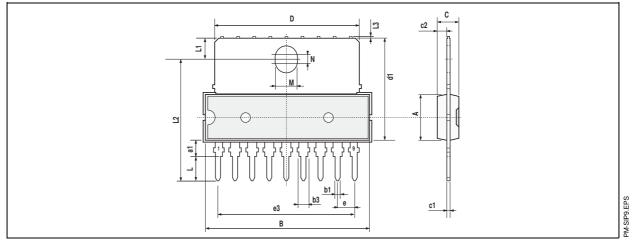

### PACKAGE MECHANICAL DATA

#### 9 PINS - PLASTIC SIP

| Dimensions |      | Millimeters |      |       | Inches |       |

|------------|------|-------------|------|-------|--------|-------|

|            | Min. | Тур.        | Max. | Min.  | Тур.   | Max.  |

| Α          |      |             | 7.1  |       |        | 0.280 |

| a1         | 2.7  |             | 3    | 0.106 |        | 0.118 |

| В          |      |             | 24.8 |       |        | 0.976 |

| b1         |      | 0.5         |      |       | 0.020  |       |

| b3         | 0.85 |             | 1.6  | 0.033 |        | 0.063 |

| С          |      | 3.3         |      |       | 0.130  |       |

| c1         |      | 0.43        |      |       | 0.017  |       |

| c2         |      | 1.32        |      |       | 0.052  |       |

| D          |      |             | 21.2 |       |        | 0.835 |

| d1         |      | 14.5        |      |       | 0.571  |       |

| е          |      | 2.54        |      |       | 0.100  |       |

| e3         |      | 20.32       |      |       | 0.800  |       |

| L          | 3.1  |             |      | 0.122 |        |       |

| L1         |      | 3           |      |       | 0.118  |       |

| L2         |      | 17.6        |      |       | 0.693  |       |

| L3         |      |             | 0.25 |       |        | 0.010 |

| М          |      | 3.2         |      |       | 0.126  |       |

| Ν          |      | 1           |      |       | 0.039  |       |

Information furnished is believed to be accurate and reliable. However, SGS-THOMSON Microelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No licence is granted by implication or otherwise under any patent or patent rights of SGS-THOMSON Microelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. SGS-THOMSON Microelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of SGS-THOMSON Microelectronics.

© 1994 SGS-THOMSON Microelectronics - All Rights Reserved

Purchase of I<sup>2</sup>C Components of SGS-THOMSON Microelectronics, conveys a license under the Philips I<sup>2</sup>C Patent. Rights to use these components in a I<sup>2</sup>C system, is granted provided that the system conforms to the I<sup>2</sup>C Standard Specifications as defined by Philips.

SGS-THOMSON Microelectronics GROUP OF COMPANIES

Australia - Brazil - China - France - Germany - Hong Kong - Italy - Japan - Korea - Malaysia - Malta - Morocco The Netherlands - Singapore - Spain - Sweden - Switzerland - Taiwan - Thailand - United Kingdom - U.S.A.

This datasheet has been download from:

www.datasheetcatalog.com

Datasheets for electronics components.